### SEE1223: Digital Electronics

#### 2 – Logic Gates and Boolean Algebra

#### **Zulkifil Md Yusof**

Dept. of Microelectronics and Computer Engineering

The Faculty of Electrical Engineering

Universiti Teknologi Malaysia

## Logic Gates and Boolean Algebra

- Logic Gates

- Inverter, OR, AND, Buffer, NOR, NAND, XOR, XNOR

- Universal Gates

- NAND and NOR

- Boolean Theorem

- Commutative, Associative, Distributive

- Basic Rules

- DeMorgan's Theorem

- Canonical/Standard Forms of Logic

- Sum of Product (SOP)

- Product of Sum (POS)

- Minterm and Maxterm

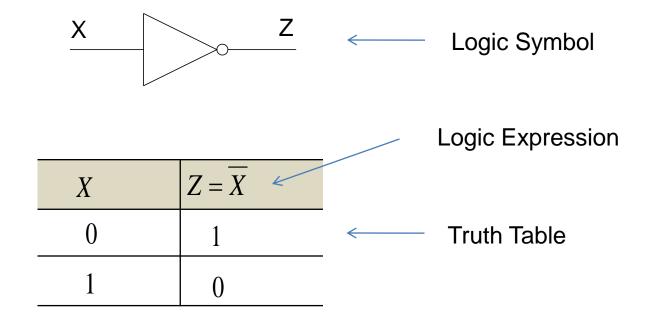

# Inverter/Not Gate

# Inverter/Not Gate

Timing Diagram

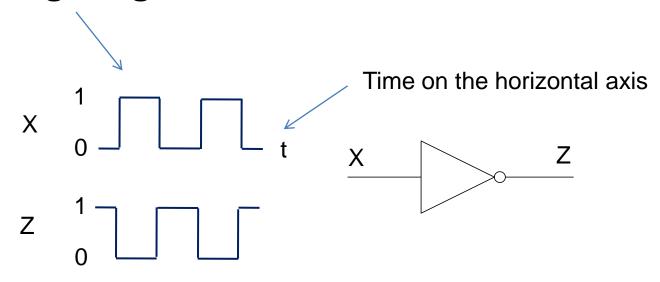

### **OR Gate**

| X | Y | Z = X + Y |

|---|---|-----------|

| 0 | 0 | 0         |

| 0 | 1 | 1         |

| 1 | 0 | 1         |

| 1 | 1 | 1         |

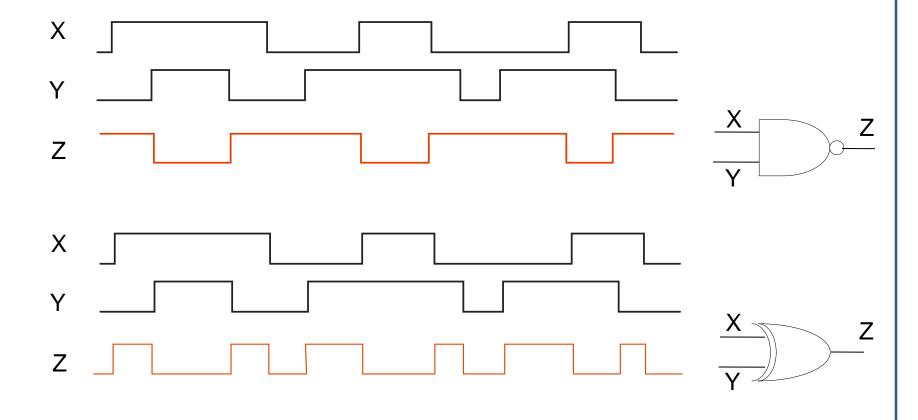

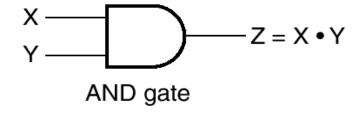

### **AND Gate**

| X | Y | $Z = X \cdot Y$ |

|---|---|-----------------|

| 0 | 0 | 0               |

| 0 | 1 | 0               |

| 1 | 0 | 0               |

| 1 | 1 | 1               |

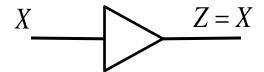

### Buffer

| X | Z = X |

|---|-------|

| 0 | 0     |

| 1 | 1     |

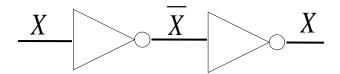

### Buffer

How to design buffers? Clue: NOT gates

- What is the use of buffers?

- Refresh weak signals

- Purposely put delays

### **XOR**

Logic Symbol and Truth Table

$$X \longrightarrow Z = X \oplus Y$$

| X | Y | $Z = X \oplus Y$ |

|---|---|------------------|

| 0 | 0 | 0                |

| 0 | 1 | 1                |

| 1 | 0 | 1                |

| 1 | 1 | 0                |

Result is '1' when exactly one input is '1'

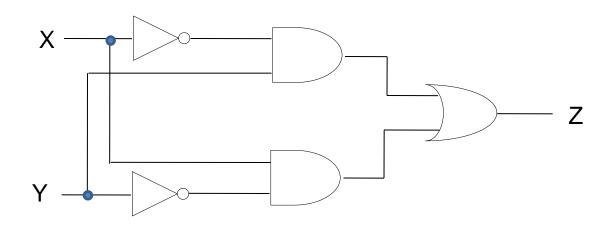

#### **XOR**

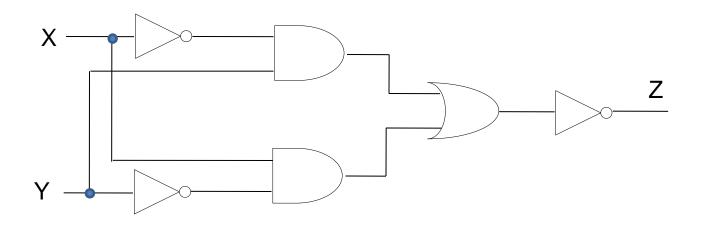

How to make XOR using basic gates (AND, OR, NOT)?

$$Z = X \oplus Y$$

$$= X \cdot \overline{Y} + \overline{X} \cdot Y$$

### **XNOR**

Logic Symbol and Truth Table

$$\begin{array}{c} X \\ Y \end{array} \longrightarrow \begin{array}{c} \\ Z = \overline{X \oplus Y} \end{array}$$

| X | Y | $Z = \overline{X \oplus Y}$ |

|---|---|-----------------------------|

| 0 | 0 | 1                           |

| 0 | 1 | 0                           |

| 1 | 0 | 0                           |

| 1 | 1 | 1                           |

Result is '1' when both inputs are the same logic

#### **XNOR**

How to make XNOR using basic gates (AND, OR, NOT)?

$$Z = X \oplus Y$$

$$= \overline{X \cdot \overline{Y} + \overline{X} \cdot Y}$$

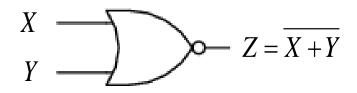

### **NOR**

Logic Symbol and Truth Table

| X | Y | $Z = \overline{X + Y}$ |

|---|---|------------------------|

| 0 | 0 | 1                      |

| 0 | 1 | 0                      |

| 1 | 0 | 0                      |

| 1 | 1 | 0                      |

Result is '1' only when both inputs are '0'

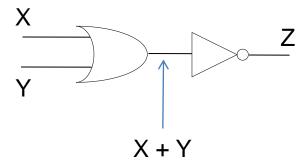

### **NOR**

How to make NOR gate using basic gates?

$$Z = \overline{X + Y}$$

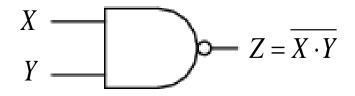

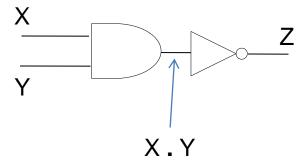

### **NAND**

Logic Symbol and Truth Table

| X | Y | $Z = \overline{X \cdot Y}$ |

|---|---|----------------------------|

| 0 | 0 | 1                          |

| 0 | 1 | 1                          |

| 1 | 0 | 1                          |

| 1 | 1 | 0                          |

Result is '0' only when both inputs are '1'

### **NAND**

How to make NAND gate using basic gates?

$$Z = \overline{X \cdot Y}$$

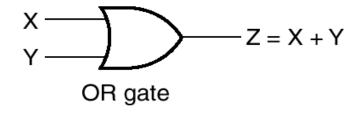

# Example

Draw the timing diagram for the following